# 6809 MICROCOMPUTER PROGRAMMING & INTERFACING WITH EXPERIMENTS

BY ANDREW C. STAUGAARD, JR.

#### The Blacksburg Continuing Education™ Series

The Blacksburg Continuing Education Series $^{TM}$  of books provide a Laboratory—or experiment-oriented approach to electronic topics. Present and forthcoming titles in this series include:

- Basic Business Software

- Circuit Design Programs for the TRS-80

- DBUG: An 8080 Interpretive Debugger

- Design of Active Filters, With Experiments

- Design of Op-Amp Circuits, With Experiments

- Design of Phase-Locked Loop Circuits, With Experiments

- Design of Transistor Circuits, With Experiments

- Design of VMOS Circuits, With Experiments

- 8080/8085 Software Design (2 Volumes)

- 8085A Cookbook

- 555 Timer Applications Sourcebook, With Experiments

- Guide to CMOS Basics, Circuits, & Experiments

- How to Program and Interface the 6800

- Microcomputer—Analog Converter Software and Hardware Interfacing

- Microcomputer Interfacing With the 8255 PPI Chip

- NCR Basic Electronics Course, With Experiments

- NCR Data Communications Concepts

- NCR Data Processing Concepts Course

- NCR EDP Concepts Course

- PET Interfacing

- Programming and Interfacing the 6502, With Experiments

- 6502 Software Design

- 6801, 68701, and 6803 Microcomputer Programming and Interfacing

- 6809 Microcomputer Programming & Interfacing, With Experiments

- TEA: An 8080/8085 Co-Resident Editor/Assembler

- TRS-80 Interfacing (2 Volumes)

In most cases, these books provide both text material and experiments, which permit one to demonstrate and explore the concepts that are covered in the book. These books remain among the very few that provide step-by-step instructions concerning how to learn basic electronic concepts, wire actual circuits, test microcomputer interfaces, and program computers based on popular microprocessor chips. We have found that the books are very useful to the electronic novice who desires to join the "electronics revolution," with minimum time and effort.

Additional information about the "Blacksburg Group" is presented inside the rear cover.

Jonathan A. Titus, Christopher A. Titus, and David G. Larsen

"The Blacksburg Group"

Bug symbol trademark Nanotran, Inc., Blacksburg, VA 24060

# 6809 Microcomputer Programming & Interfacing, With Experiments

by Andrew C. Staugaard, Jr. Copyright © 1981 by Andrew C. Staugaard, Jr.

FIRST EDITION

FIRST PRINTING—1981

All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission from the publisher. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 0-672-21798-6 Library of Congress Catalog Card Number: 81-50567

Printed in the United States of America.

#### **Preface**

Welcome to the world of *advanced* microprocessors! In the early seventies we witnessed the dawn of a second industrial revolution with the introduction of first-generation programmable logic devices. These "smart" devices on a single piece of sand (silicon chip) were appropriately called *microprocessors*. They revolutionized the engineering of many everyday products, from toys and appliances to the automobile and large computer systems.

In the past few years the microprocessor chip industry has exploded into a multibillion dollar business. As stated in the June 30, 1980, issue of Newsweek magazine, "The explosion is just beginning. In 1979, the world market for microelectronics topped \$11 billion. Over the next five years, chip sales are expected to grow by at least 20 percent annually, and the market for microprocessors 'computers on a chip' will expand by 50 percent each year—even though the chips themselves and the computing power they represent are diving in price."

Two large microprocessor application markets have emerged—the *dedicated* market and the *systems* market. The resources of the first-and second-generation devices, such as the 6800, 8080, and Z-80, were made to satisfy both market applications. Each market, however, requires separate microprocessor features for efficient utilization of the device. For example, the dedicated market requires a device which incorporates many functions such as CPU, R/W memory, ROM/EPROM, timer, serial i/o, etc., onto *one* chip to minimize the chip count for such applications as the automobile, appliances, machine tool control, toys, etc. The systems market, on the other hand, requires a very powerful software device such that high-level language programming can be efficiently implemented. Most micro-

processor chip manufacturers have taken these two directions in their newer-generation chip designs. In the Motorola family the 6801 and 6805 satisfy the dedicated market applications, with the 6809 and 68000 having been designed particularly for the systems market.

The 6809 is a high-performance 8-bit microprocessor. It has many very powerful software features which are particularly useful for high-level language (Pascal, FORTRAN, BASIC, COBOL, etc.) implementation. In fact, as you are about to discover, the 6809 approaches the performance of many 16-bit devices, such as the 8086, Z-8000, and 68000, without the inherent overhead costs required to engineer such a 16-bit system. Flexible 8-bit devices, like the 6809, will be around for many years to come despite the onslaught of the 16-bitters, since many applications do not require such high performance. In addition, when 16-bit systems do become common, they

This book is meant to be a tutorial type of text for a first exposure will rely on 8-bit devices to perform many dedicated tasks such as peripheral control, data acquisition, etc.

to the 6809 or to high-performance microprocessors in general. I am confident that you will also find it extremely valuable as a "cookbook" type aid when you are working with the 6809. Since the 6809 is a "souped up" 6800, a basic understanding of the 6800 will be assumed throughout the text. If a review is needed, you may wish to consult my *How to Program and Interface the 6800*, published by Howard W. Sams & Co., Inc.

A set of objectives is provided in the first part of each chapter, with review questions and answers provided at the end of each chapter. There are also numerous examples that illustrate the text. I encourage you to study the examples in detail, since many of the important software concepts are demonstrated within the example programs. I also encourage you to pay particular attention to Chapter 2, "6809 Addressing Modes." You will find that the *secret* to understanding the 6809 software concepts is understanding its 19 addressing modes.

Finally, I would like to express my appreciation to Motorola Semiconductor Products at Austin, Texas, and Phoenix, Arizona, for their technical assistance and permission to use their 6809 documentation in this text.

Andrew C. Staugaard, Jr.

To my mother and father, who provided me the good home life and education required to be successful in today's world. And to one of my best friends, my father in law, Zane Benefiel, whose encouragement in my early professional days led to the completion of this and two previous manuscripts.

## **Contents**

**CHAPTER 1**

| Fundamental 6809 Concepts and Chip Structure                                                                                                                                                                                          | 7  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Introduction—Objectives—6809 Evolution and Design Philosophy—6809 Improvements—6809 Chip Structure—Review Questions—Answers                                                                                                           |    |

| CHAPTER 2                                                                                                                                                                                                                             |    |

| 6809 Addressing Modes                                                                                                                                                                                                                 | 23 |

| Introduction—Objectives—Inherent, Immediate, and Extended Addressing—Direct Addressing and the Direct Page Register Relative Addressing—Indexed Addressing—Post Byte—Indirect Addressing—Register Addressing—Review Questions—Answers |    |

| CHAPTER 3                                                                                                                                                                                                                             |    |

| 6809 REGISTERS AND DATA MOVEMENT INSTRUCTIONS                                                                                                                                                                                         | 51 |

| Introduction — Objectives — 6809 Internal Register Format — Data Movement Instructions—Review Questions—Answers                                                                                                                       |    |

| CHAPTER 4                                                                                                                                                                                                                             |    |

| ARITHMETIC, LOGIC, AND TEST INSTRUCTIONS                                                                                                                                                                                              | 73 |

| Introduction—Objectives—Arithmetic Instructions—Logic Instructions—Test Instructions—Review Questions—Answers                                                                                                                         |    |

| CHAPTER 5                                                                                                                                                                                                                             |    |

| Branch and Miscellaneous Instructions                                                                                                                                                                                                 | 93 |

| Introduction — Objectives — Branch Instructions — Miscellaneous Instructions—Review Questions—Answers                                                                                                                                 |    |

#### **CHAPTER 6**

| 6809/6809E INPUT AND OUTPUT SIGNALS                                                                                                                                | 115 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Introduction—Objectives—6809 Pin-Outs—6809E Pin-Outs—Review Questions—Answers                                                                                      |     |

| CHAPTER 7                                                                                                                                                          |     |

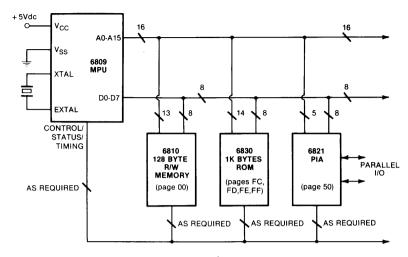

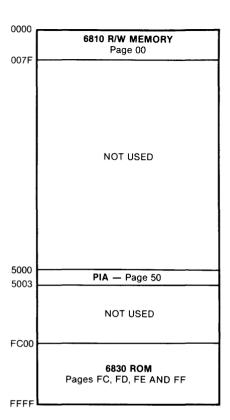

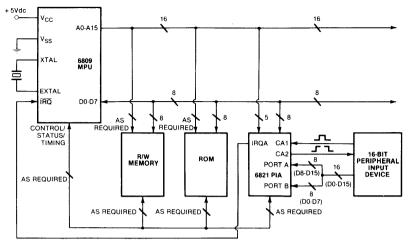

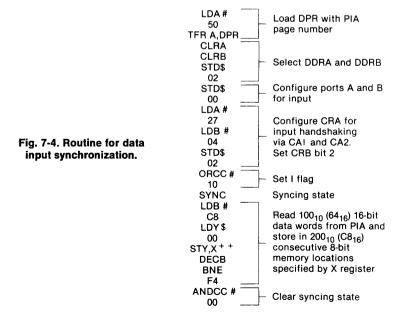

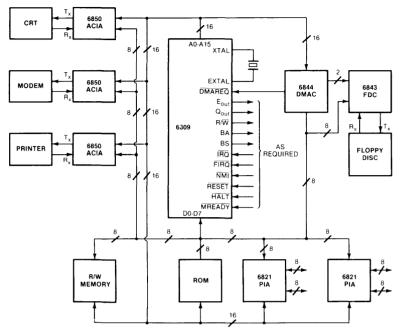

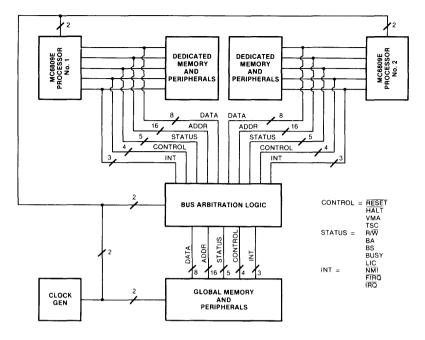

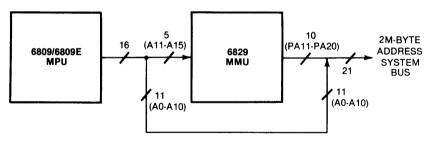

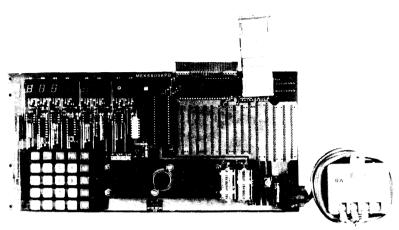

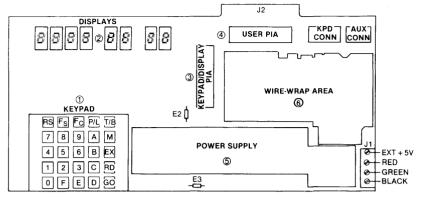

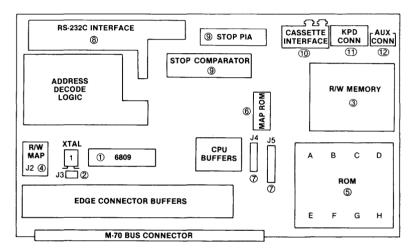

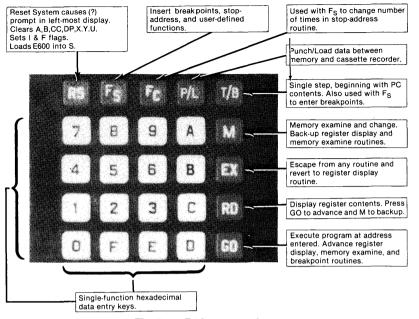

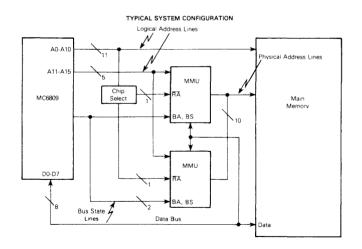

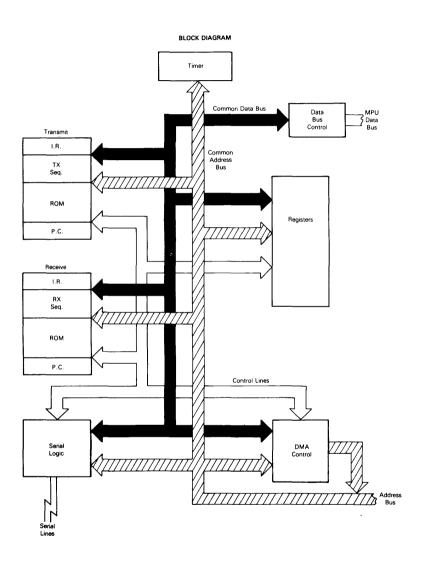

| 6809/6809E Interfacing and Applications                                                                                                                            | 140 |

| Introduction—Objectives—A Minimum 6809 System—An Expanded 6809 System—Multiprocessor Systems—Remote Data Acquisition—The MEK6809D4 Microcomputer Evaluation System |     |

| APPENDIX A                                                                                                                                                         |     |

| 6809/6809E Instruction Set                                                                                                                                         | 163 |

| Operation Notation—Register Notation—Definitions of Executable Instructions                                                                                        |     |

| APPENDIX B                                                                                                                                                         |     |

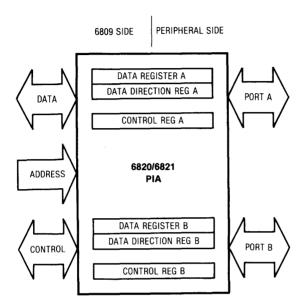

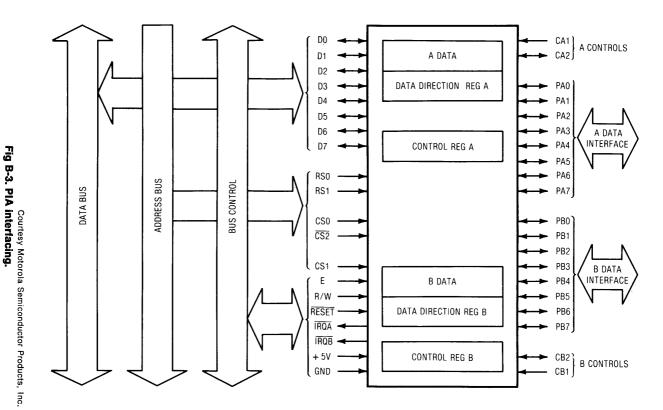

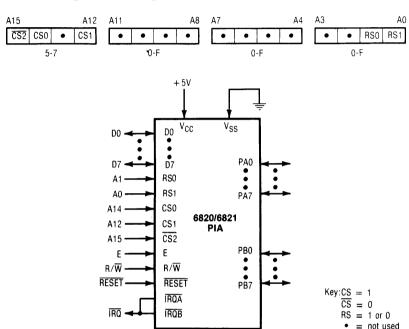

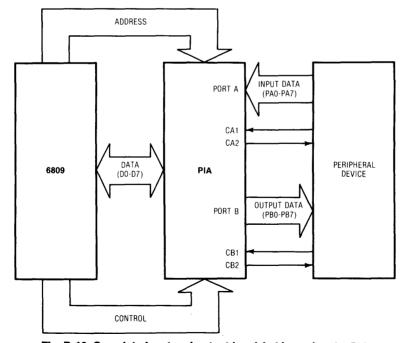

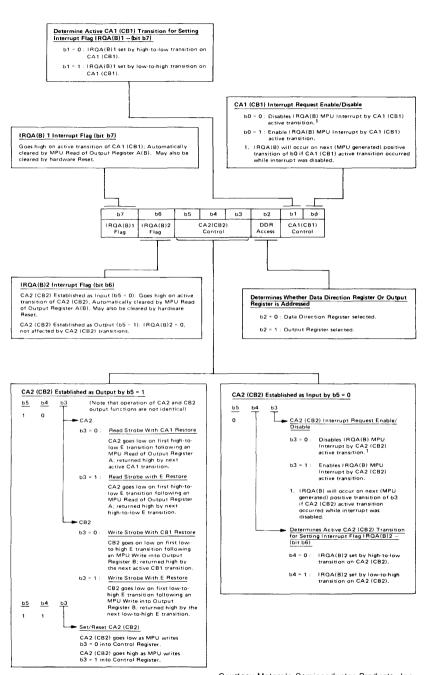

| The 6820/6821 Peripheral Interface Adapter (PIA)                                                                                                                   | 192 |

| 6821 Functional Description—6820/6821 Pin Assignments—PIA Interfacing and Addressing—PIA Initialization and Servicing—Review Questions—Answers                     |     |

| APPENDIX C                                                                                                                                                         |     |

| Specification Sheets                                                                                                                                               | 211 |

| MC6809/MC68A09/MC68B09-MC6809E/MC68A09E/MC68B09E<br>-MC6829 - MC6839 - MC6842 - MEK6809AC - MEK6809D4/<br>MEK68KPD                                                 |     |

| APPENDIX D                                                                                                                                                         |     |

| MC6809 Instruction Set Summary                                                                                                                                     | 256 |

| Index                                                                                                                                                              | 268 |

#### CHAPTER 1

# Fundamental 6809 Concepts and Chip Structure

#### INTRODUCTION

As you will discover in this and subsequent chapters, the 6809 is one of the most powerful 8-bit processors to come on the market to date. In conceiving the 6809 the Motorola design engineers wanted to maintain compatibility with the popular 6800 at some level, yet "soup up" the 6800 architecture and instruction set to approach the performance of a 16-bit processor, such as the 68000 or Z-8000. From user surveys Motorola concluded that many customers desired such performance from an 8-bit, 40-pin device. It was found that many users did not want to pay the price for conversion to a 16-bit device with up to 64 pins if a high-performance 8-bit device were available. Therefore, the 6809 was designed to approach 16-bit performance at minimum cost to the user.

In this chapter we begin by discussing the 6809 evolution and design philosophy. You will see that the 6809 has been designed primarily for the systems market, where high-level language implementation is common. Throughout the discussion, comparisons will be made between the 6809, 6800, and other competitive processors. In addition, as an introduction to subsequent chapters, this chapter will summarize the 6809's architecture, software, and hardware. It is important that you understand what improvements have been made in the 6809 over the 6800 since this will enable you to better understand the material to follow.

#### **OBJECTIVES**

At the end of this chapter you will be able to do the following:

- Explain the evolution of the 6800 family.

- Understand the design philosophy that created the 6809.

- State the differences between the 6809 68A09 68B09 and 6809E

- List the additional registers present in the 6809 that do not exist in the 6800.

- Describe the two additional condition code flags available in the

- Define indirect addressing.

- Compare 6809 branching to 6800 branching.

Explain what is meant by "memory paging" and how this is accomplished with the 6809.

- Describe the fundamental hardware differences between the 6809 and 6800.

- Explain the difference between a standard interrupt request and a fast interrupt request.

#### 6809 EVOLUTION AND DESIGN PHILOSOPHY

As stated in the introduction to this chapter the 6809 was designed to upgrade or "soup up" the 6800 to be superior to any 8-bit microprocessor. Also, Motorola wanted to capitalize on their customers' familiarity with the 6800 so that exposure to the 6809 would not create severe learning problems for those 6800 users. Therefore this design philosophy dictates that the fundamental 6800 architecture be used as a basis for the 6809 architecture and that software compatibility be available at some level. As you will discover in Chapter 3 this compatibility exists at the source code (mnemonic) level and not the object code (op-code) level. You will also discover that the 6809 does not contain dozens of new instructions. However, it uses over three times as many addressing modes as the 6800 to provide more efficient utilization of the existing instructions. The power of a processor is not a function of the number of unique instructions available in its instruction set. The real power of a processor lies in how many different ways a given instruction can operate on the same data and also how the given instruction set can operate on different data in the same manner. This flexible instruction power is provided by the different addressing modes available to the fundamental instruction set. The 6809 uses its 19 addressing modes in conjunction with 59 fundamental instructions to provide a total of 1464 unique operations. Motorola believes that the 6809 contains the most powerful addressing modes available in any microprocessor to date.

Since the 6809 is primarily designed for the systems market, program position independence, program re-entrancy, and easy implementation of block-structured high-level languages (such as Pascal)

were also prime design considerations. These terms have the following meanings:

- program position independence—that quality of a program to execute properly when placed anywhere within the memory address map. Thus the program is independent of its position within the memory map.

- program re-entrancy—that quality of a program which allows a subroutine to be shared by several tasks concurrently, without destroying the return addresses by nesting routines.

With position independence, programs can be loaded from a mass storage disc and located anywhere within R/W memory without requiring the use of a relocating loader routine. In addition, position independence will allow ROM programs to be written for general distribution. The user can assign any arbitrary set of addresses to the ROM since the program execution is "independent" of its position within the memory map. This will eliminate the necessity for full ROM address decoding and will also allow the user to locate the ROM such that it will not interfere with other software. As you will see shortly, the advanced 6809 architecture also facilitates the use of modular programming. Such programming will allow the system software designer to divide a project up into modular programs which can be designed and tested independently before being incorporated into the final system design. This same architecture allows programs to be structured and interrupted in any part of the address map and still execute properly on return, thus satisfying the program re-entrancy design goal. In addition, high-level blockstructured languages, such as Pascal, BASIC, FORTRAN, and COBOL, can be compiled into more efficient and faster-running machine code than was possible with earlier processors.

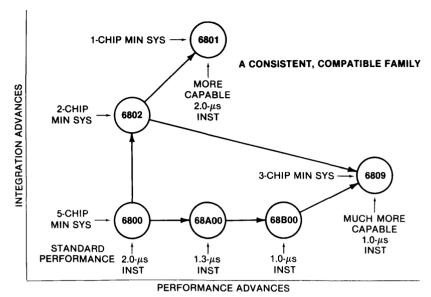

The 6800 family evolution scheme is shown in Fig. 1-1. Note the position of the 6809. As far as central processing unit (CPU) performance is concerned the 6809 is the most advanced processor in the Motorola 8-bit family. However, the 6809, by itself, is a microprocessor and not a microcomputer. It requires external R/W memory and ROM to function as a microcomputer. Therefore a minimum 6809 system would consist of three chips. Recall from our discussion in the Preface that microprocessor/microcomputer applications take two directions: small, dedicated applications and systems applications. In the 8-bit Motorola family the 6809 satisfies the needs of the latter, while the 6801, 6802, 6803, and 6805 were designed for the dedicated applications. These four devices all contain various amounts of R/W memory, ROM, and parallel/serial i/o capabilities. They are therefore more advanced as far as chip integration is concerned since some or all of these capabilities are integrated into the

Fig. 1-1. M6800 family evolution.

same chip, along with the CPU. For example, the 6801 contains an enhanced 6800 CPU, R/W memory, ROM, timer, parallel interfacing ports, and a serial port, all on one 40-pin chip. Hence, we say that the 6801 is a "single-chip" microcomputer.\* The 6809, however, is a far more advanced processor, approaching 16-bit performance.

As you will see in Chapter 6, the standard 6809 does contain an on-chip clock/oscillator and therefore only requires an external crystal to provide the clock signal. The standard 6809 operates at 1 MHz. However, it is also available in 1.5-MHz and 2.0-MHz versions: the 68A09 and 68B09, respectively. In addition, there is an off-chip clock version of the 6809 available, the 6809E.

Now let's compare the performance of the 6809 to the 6800 and some other well-known processors. Compared to the 6800, the 6809 boasts the following performance:

- 72 percent decrease in the number of instructions required for a program compared to similar 6800 programs.

- 58 percent decrease in the required program memory compared to 6800 programs.

- 167 percent increase in 6809 processor throughput compared to 6800 throughput.

<sup>\*</sup> For a detailed discussion of the 6801/68701 and 6803 consult Staugaard, A.C. 6801/68701 and 6803 Microcomputer Programming and Interfacing, published by Howard W. Sams & Co., Inc., Indianapolis.

Motorola claims that these statistics allow the user to achieve 2.5 to 5 times the performance from a 6809 system compared with a similar 6800-based system. Of course, the exact amount of increased performance depends on how efficiently the increased capabilities of the 6809 are utilized and on the specific application.

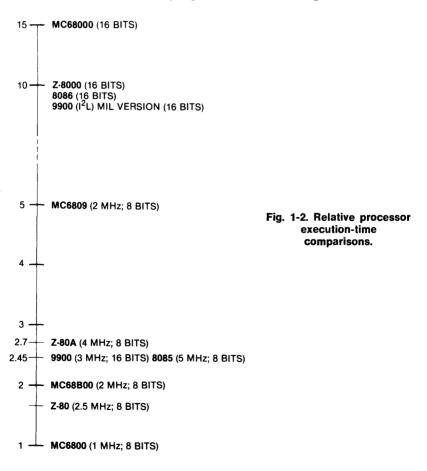

Comparisons of the 6809 to the 6800 and other processors are summarized in Fig. 1-2 and in Tables 1-1 through 1-3. Note, especially from Fig. 1-2, that the 6809 approaches 16-bit performance. The comparison values in these tables and Fig. 1-2 were supplied by Motorola and thus tend to illustrate the better aspects of the 6809 over the other processors.

#### 6809 IMPROVEMENTS

The increased performance of the 6809 over other 8-bit processors is made possible by specific improvements in architecture, software, and hardware. Each of the following improvements over the 6800 is discussed in detail in subsequent chapters; however, we will summarize them here.

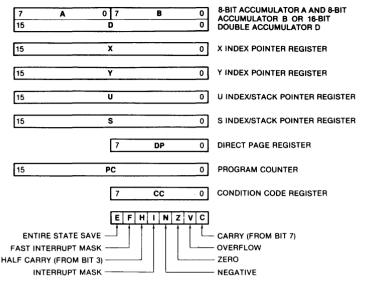

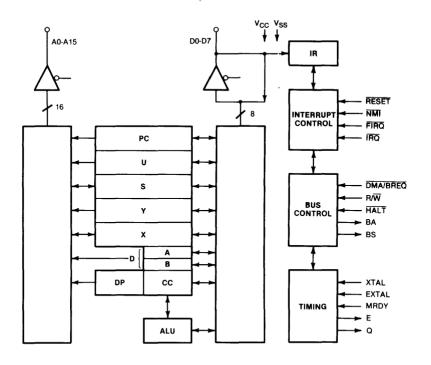

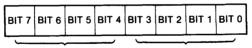

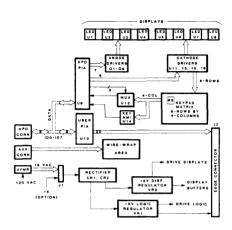

#### **Architectural Improvements**

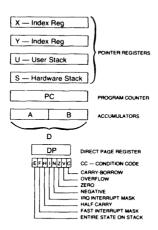

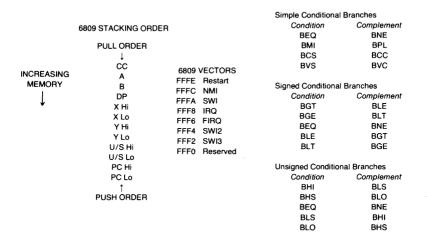

Compared with the 6800 architecture the 6809 adds an 8-bit register and three 16-bit registers as shown in Fig. 1-3. The additional 8-bit register is the direct page register, which will allow you to use the direct addressing mode anywhere within the 6809 memory map. (Recall that direct addressing is limited to the first 256 bytes of memory with the 6800.) The three additional 16-bit registers include a 16-bit accumulator, index register, and stack pointer. The additional accumulator is referred to as accumulator D and is simply the concatenation of the two 8-bit accumulators, A and B. The additional index register is called the Y index register (Y) and the additional stack pointer is referred to as the user stack pointer (U). The two index registers, X and Y, will also function as pointers and the two stack pointers (S and U) can be used for indexing.

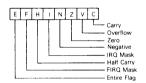

In addition, you will note from Fig. 1-3 that all 8 bits of the condition code register (CC) are being used in the 6809. Recall that only the first 6 bits are utilized in the 6800. The functions of the first 6 CC bits (C, V, Z, N, I, H) in the 6809 are identical with those of the 6800. The two additional bits (F and E) are used in conjunction with the 6809's interrupts. The use of these two additional bits will be discussed in detail in subsequent chapters.

These architectural improvements along with the 6809's powerful addressing modes speed processor throughput, since less data movement is required between the internal registers and memory, and

Table 1-1. Relative Processor Execution-Time Comparisons for Eight Software Operations

|      |         | I/O<br>Handler | Character<br>Search | Computed<br>Go To | Double<br>Shift<br>Right<br>5 Bits | Vector<br>Addition<br>16-Bit<br>Elements | Vector<br>Addition<br>8-Bit<br>Elements | 16 × 16-Bit<br>Multiplication | Move Block<br>(64 Bytes) | Average<br>Execution<br>Time |

|------|---------|----------------|---------------------|-------------------|------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------|--------------------------|------------------------------|

| 6809 | 2.0 MHz | 1.0            | 1.0                 | 1.0               | 1.0                                | 1.0                                      | 1.0                                     | 1.0                           | 1.0                      | 1.0                          |

|      | 1.5 MHz | 1.3            | 1.3                 | 1.3               | 1.3                                | 1.3                                      | 1.3                                     | 1.3                           | 1.3                      | 1.3                          |

|      | 1.0 MHz | 2.0            | 2.0                 | 2.0               | 2.0                                | 2.0                                      | 2.0                                     | 2.0                           | 2.0                      | 2.0                          |

| Z-80 | 4.0 MHz | 1.4            | 0.8                 | 2.1               | 2.7                                | 1.6                                      | 1.8                                     | 3.3                           | 1.0                      | 1.8                          |

|      | 2.5 MHz | 2.2            | 1.2                 | 3.4               | 4.4                                | 2.6                                      | 2.9                                     | 5.2                           | 1.6                      | 2.9                          |

| 9900 | 3.0 MHz | 2.6            | 2.3                 | 2.8               | 1.5                                | 1.7                                      | 3.0                                     | 0.5                           | 1.6                      | 2.0                          |

| 6800 | 2.0 MHz | 0.9            | 1.4                 | 1.9               | 1.3                                | 3.1                                      | 2.8                                     | 5.0                           | 3.3                      | 2.4                          |

|      | 1.5 MHz | 1.2            | 1.9                 | 2.5               | 1.7                                | 4.1                                      | 3.7                                     | 6.7                           | 4.3                      | 3.3                          |

|      | 1.0 MHz | 1.8            | 2.8                 | 3.7               | 2.5                                | 6.1                                      | 5.5                                     | 10                            | 6.5                      | 4.9                          |

| 8080 | 3.0 MHz | 1.9            | 1.8                 | 2.8               | 6.1                                | 2.3                                      | 2.7                                     | 9.6                           | 2.4                      | 3.7                          |

| 8085 | 2.0 MHz | 2.8            | 2.6                 | 4.2               | 9.1                                | 3.4                                      | 4.1                                     | 14.3                          | 3.7                      | 5.5                          |

Table 1-2. Actual Processor Execution-Time Comparisons for Eight Software Operations

|      |         |                |                     |                   | -                                  |                                          | -                                       | •                             |                          |

|------|---------|----------------|---------------------|-------------------|------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------|--------------------------|

|      |         | I/O<br>Handler | Character<br>Search | Computed<br>Go To | Double<br>Shift<br>Right<br>5 Bits | Vector<br>Addition<br>16-Bit<br>Elements | Vector<br>Addition<br>8-Bit<br>Elements | 16 × 16-Bit<br>Multiplication | Move Block<br>(64 Bytes) |

| 6809 | 2.0 MHz | 28             | 287.5               | 34.5              | 15                                 | 325                                      | 180                                     | 82                            | 344.5                    |

|      | 1.5 MHz | 37.3           | 383                 | 46                | 20                                 | 433                                      | 240                                     | 109.3                         | 459.3                    |

|      | 1.0 MHz | 56             | 575                 | 69                | 30                                 | 650                                      | 360                                     | 164                           | 689                      |

| Z-80 | 4.0 MHz | 38.3           | 220.5               | 73.3              | 41                                 | 518                                      | 323                                     | 267                           | 342                      |

|      | 2.5 MHz | 61.3           | 352.8               | 117.2             | 65.6                               | 828.8                                    | 516.8                                   | 427.2                         | 547.6                    |

| 9900 | 3.0 MHz | 72             | 661                 | 98                | 22                                 | 537                                      | 537                                     | 42                            | 537                      |

| 6800 | 2.0 MHz | 24.5           | 404                 | 64.5              | 19                                 | 993.5                                    | 498.5                                   | 409.5                         | 1123.5                   |

|      | 1.5 MHz | 32.7           | 539                 | 86                | 25.3                               | 1325                                     | 665                                     | 546                           | 1498                     |

|      | 1.0 MHz | 49             | 808                 | 129               | 38                                 | 1987                                     | 997                                     | 819                           | 2247                     |

| 8080 | 3.0 MHz | 52.7           | 506.7               | 96.7              | 91.3                               | 732                                      | 492                                     | 784                           | 841                      |

| 8085 | 2.0 MHz | 79             | 760                 | 145               | 137                                | 1098                                     | 738                                     | 1176                          | 1262                     |

Table 1-3. Summarized Processor Performance Comparisons

| Performance Criteria   | MC6809  | Z-80A   | MC6800  | 8085    |

|------------------------|---------|---------|---------|---------|

| Number of Instructions | 1.0*    | 1.56    | 1.72    | 2.30    |

| Number of Bytes        | 1.0     | 1.31    | 1.58    | 1.80    |

| Number of Microseconds | 1.0     | 1.80    | 2.40    | 2.20    |

|                        | (2 MHz) | (4 MHz) | (2 MHz) | (5 MHz) |

<sup>\*</sup>Normalized to 1.00 for the MC6809 - poorer performance has higher numbers.

they also aid software development since many of the internal registers can be made to perform different functions at different times.

#### **Software Improvements**

Improvements in the 6809's architecture have allowed the Motorola designers to make many significant software improvements over

Fig. 1-3. 6809 internal registers.

the 6800. In fact, the 6809 has been termed "the programmer's dream machine." Prior to firm definition of the 6809 instruction set Motorola conducted a survey of 6800 users to determine: (1) if a 16-bit architecture was more desirable than an 8-bit architecture and (2) should 6809 compatibility with the 6800 occur at the object code level or source code level? The survey results indicated that most of the 6800 users felt that an 8-bit architecture was adequate for their future applications. They did not want to pay the price for a new 16-bit device if an 8-bit device could be designed to perform common 16bit operations, such as load, store, add, subtract, compare, and multiply. As you will discover in Chapter 3, the inclusion of the 16-bit accumulator and associated instructions will allow such 16-bit operations to be performed internally. In answer to the second survey question, almost all of the responses indicated that source code compatibility would be adequate, mainly because they did not foresee using 6800 ROMs in future 6809 systems. Source code compatibility meant that users could take full advantage of their familiarity with the 6800 mnemonic code for assembly language programming and it also allowed the 6809 designers to completely remap or reassign the 6800 op codes to produce more efficient and faster running 6809 programs. Also, source code compatibility would allow any 6800 programs to be processed through a 6809 assembler to produce 6809 code. Therefore, you will see a familiar mnemonic code in Chapters 3, 4, and 5; however, most of the corresponding op codes are different from those of the 6800.

As mentioned earlier, the 6809 adds many new and powerful addressing modes. For example, the indexed mode of addressing can use the four 16-bit indexible registers (X, Y, U, and S) to point to the address of an operand or to the address of the address of an operand. The latter is referred to as indirect addressing. These registers can also be incremented and decremented automatically or under program control. The 6809 can even use the program counter to access operands or operand addresses. Furthermore, with the use of the direct page register, you can access any part of the 6809 memory map using direct addressing. You can also branch to any part of the program using relative addressing. Recall that with the 6800, you were limited to a plus 127<sub>10</sub> and minus 128<sub>10</sub> branch range within the program, since the relative address offset is only 1 byte. However, the 6809 allows for a 2-byte relative address offset and thus permits branching anywhere within the 64K memory map (long branch). This allows position-independent programs to be written for the 6809. We will discuss the idea of position independence in more detail when discussing relative addressing.

Other software features of the 6809 include:

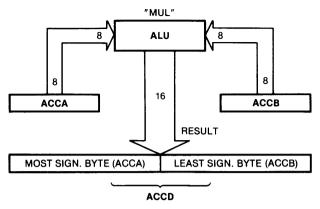

- An 8 × 8 unsigned multiply instruction which generates a 16-bit result.

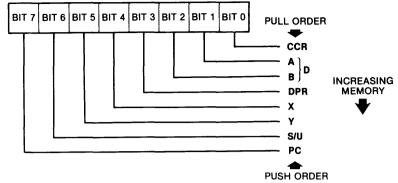

- 2-byte instructions which will push or pull any or all registers onto or from either stack (U or S).

- 16-bit add, subtract, load, store, and compare instructions which utilize the 16-bit accumulator (D).

- Instructions which permit you to add any of the accumulators (A, B, or D) to any of the index registers and stack pointers (X, Y, S, or U).

- Instructions which permit you to perform exchanges and transfers between any two like-size CPU registers.

#### **Hardware Improvements**

Besides the architectural and software improvements of the 6809 over the 6800, many hardware improvements were also made. Most of these improvements involve the 6809's interrupts, control signals, and associated control lines. We will summarize these new hardware features here; however, a complete discussion of the 6809 pin-outs and associated chip operation is provided in Chapter 6.

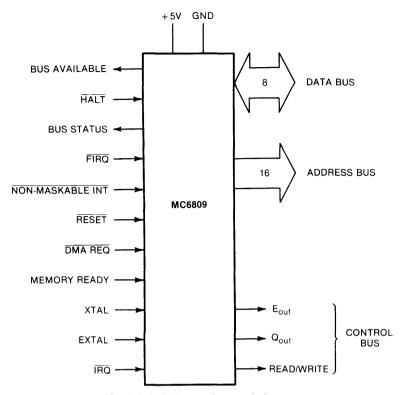

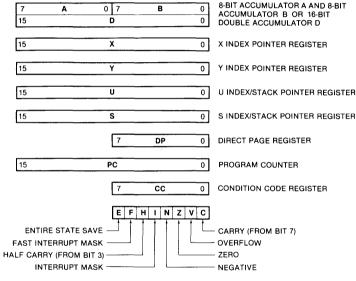

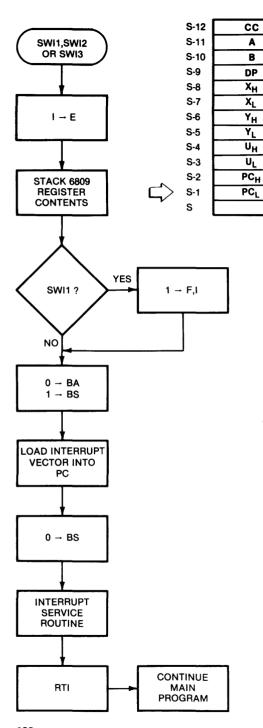

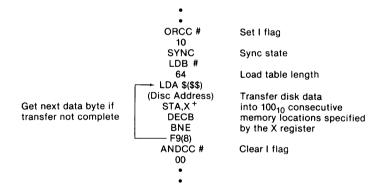

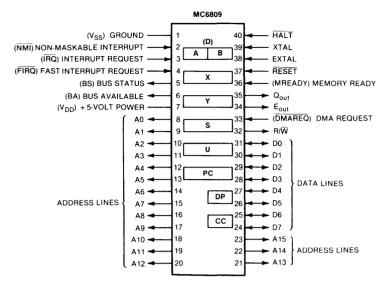

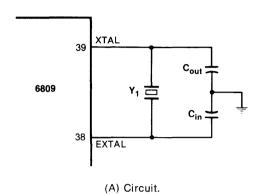

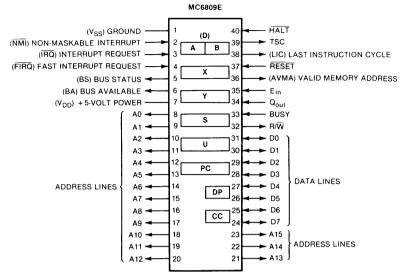

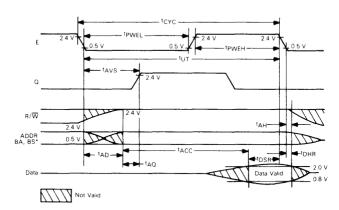

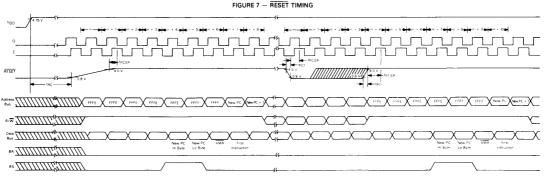

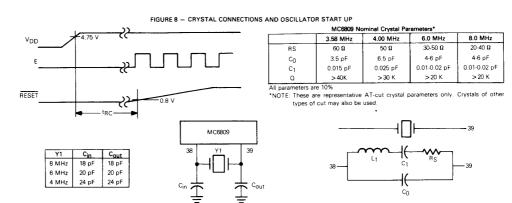

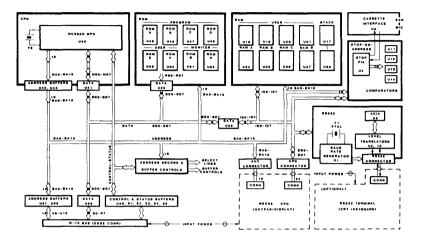

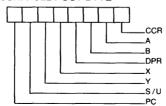

Like the 6800, the 6809 is a 40-pin device available in both a plastic (P-suffix) and ceramic (L-suffix) package. A bus and control signal diagram for the 6809 is shown in Fig. 1-4. The most obvious change to the chip hardware is the inclusion of an on-chip clock/oscillator for the standard 6809 package. (Recall that the 6809E is an off-chip clock version of the 6809.) The 6809 on-chip clock re-

Fig. 1-4. 6809 bus and control signals.

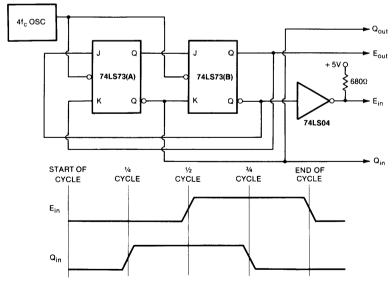

quires only the addition of an external crystal (EXTAL and XTAL) to establish the internal clock frequency. The crystal frequency must be four times (4×) the desired internal clock frequency. Therefore, to achieve a 1-MHz operation, a 4-MHz crystal must be used. This has been done to create a more cost-effective system since an inexpensive 3.58-MHz tv color-burst crystal can be used, resulting in a 0.895-MHz clock frequency, without seriously affecting the chip performance.

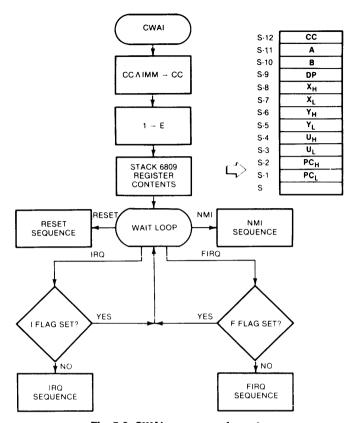

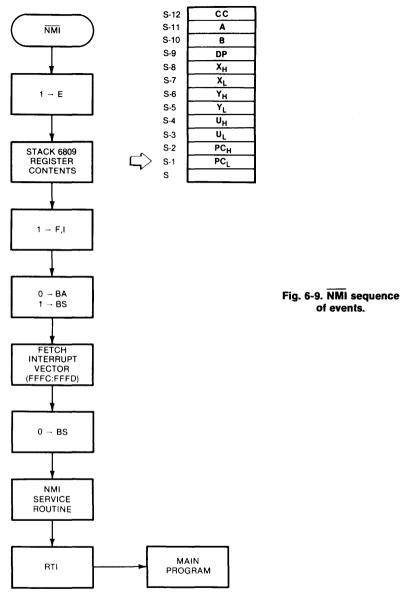

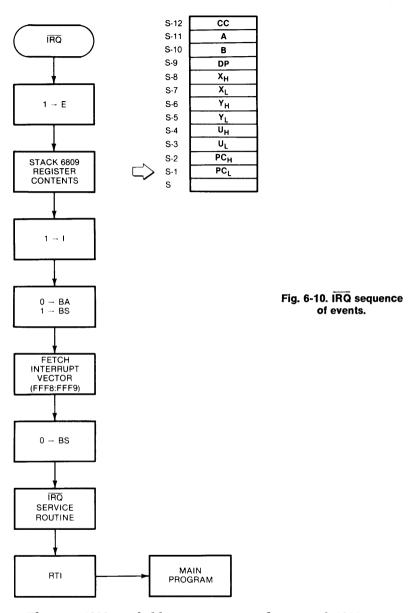

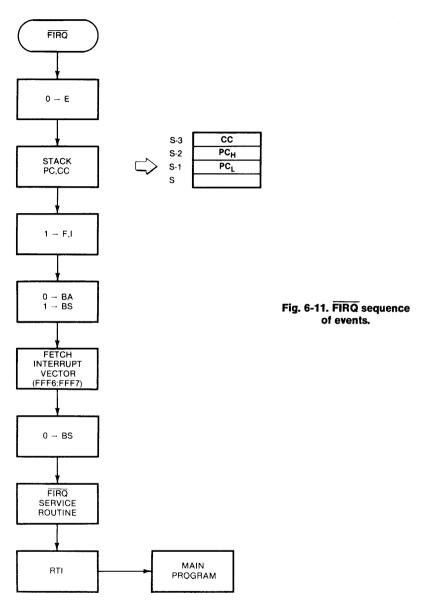

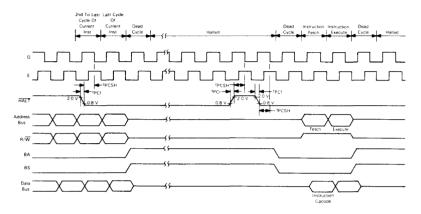

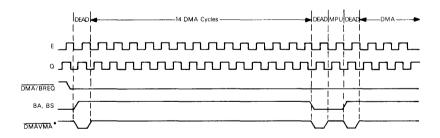

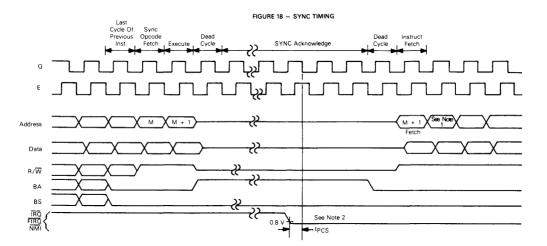

The new control features of the 6809 include a fast interrupt request ( $\overline{FIRQ}$ ), bus status (BS), quadrature clock (Q), memory ready (MRDY), and direct memory access request ( $\overline{DMA}$  REQ) control signals. You will use the fast interrupt request ( $\overline{FIRQ}$ ) line when it is known that the interrupt routine will use existing register data. Thus, with the fast interrupt, all the registers are not stored unnecessarily requiring extra time; only the program counter and condition code register are saved. However, as you will discover in Chapter 6, you can also use  $\overline{FIRQ}$  to initiate a standard interrupt request where the contents of all the internal registers are saved.

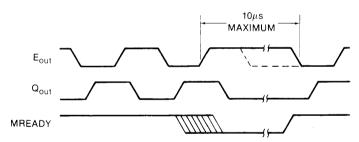

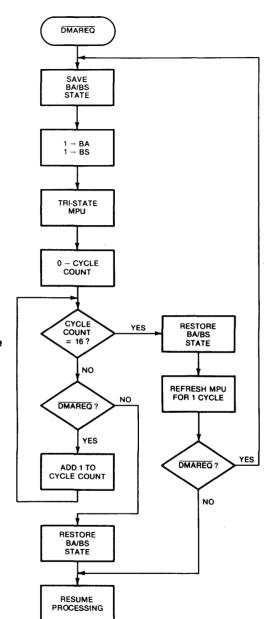

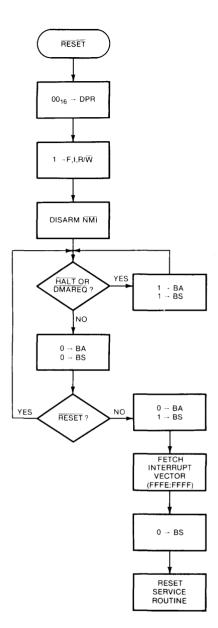

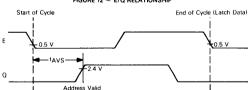

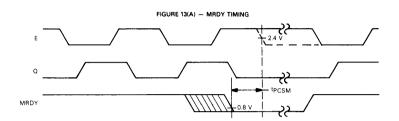

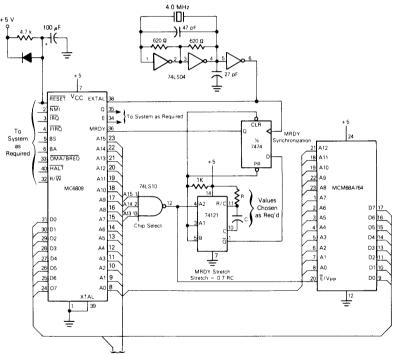

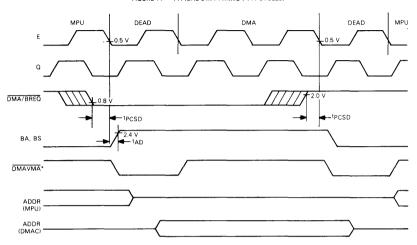

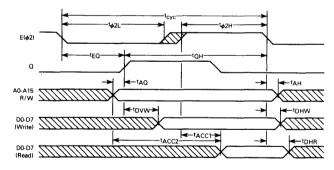

The new bus status (BS) line is used in conjunction with the bus available (BA) line to indicate bus status and provide an interrupt acknowledge. The quadrature clock (Q) is a clock signal which leads the enable clock signal (E) by one-quarter cycle (90°). Enable (E) is the same as the 6800's  $\phi$ 2 clock signal. Valid addresses are available from the 6809 on the leading edge of Q, with data being latched on the trailing edge of E. These two external clock signals provide four effective system timing edges for interfacing purposes. The memory ready line (MRDY) is for interfacing with slow memories. This input control signal effectively stretches the E pulse to extend data-access time. Finally, the direct memory access request line (DMA REQ) is an input control line which provides a method for suspending processor execution and freeing the external buses for other purposes, such as direct memory access by a peripheral device or dynamic memory refresh.

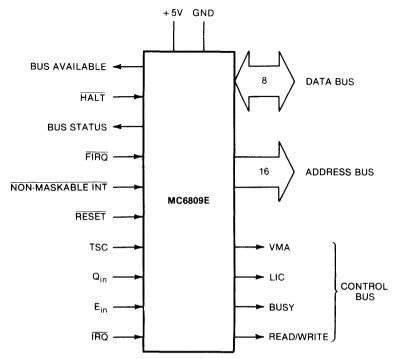

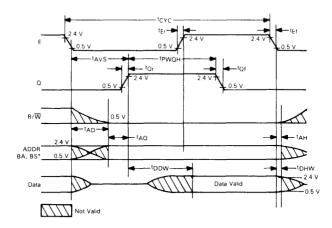

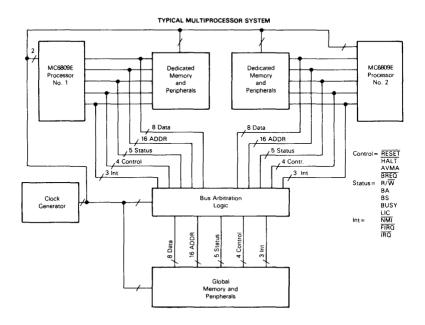

A bus and control signal diagram for the 6809E is shown in Fig. 1-5. Since the 6809E does not require an external crystal connection, two additional control signals are added. They are: Busy, and Last Instruction Cycle (LIC). Since these two control signals are avail-

Fig. 1-6. 6809 chip structure.

Fig. 1-5. 6809E bus and control signals.

able, the 6809E is ideally suited for multiprocessor applications. Busy is an output control line which indicates that the 6809E is accessing memory and the last instruction cycle (LIC) signal alerts external devices to the fact that the 6809E is executing the last cycle of an instruction.

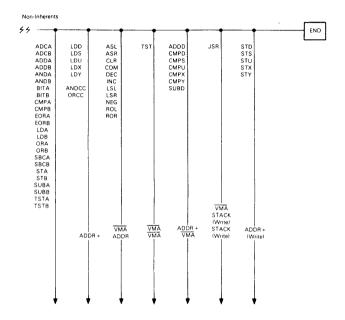

If you are familiar with the 6800, note that the standard 6809 does not include two control lines that are available on the 6800. They are the valid memory address (VMA) and three-state control (TSC) signals. Recall that VMA was required in external device interfacing to provide proper device selection. Therefore, the elimination of this signal eliminates the gating required to use it for external device selection. Instead of using VMA to indicate a valid address exists on the address bus, the 6809 places FFFF on the address bus during any clock cycle when it is not using the bus structure. The three-state control line (TSC) is simply replaced by the  $\overline{\rm DMA~REQ}$  line on the 6809. The 6809E, however, uses both VMA and TSC (Fig. 1-5).

Finally, there is one other subtle hardware difference between the 6800 and 6809. Both the 6809 and 6809E contain a Schmitt trigger input on the RESET interrupt such that a simple RC circuit is all that is required to reset the processor during "power up." This is not included in the 6800.

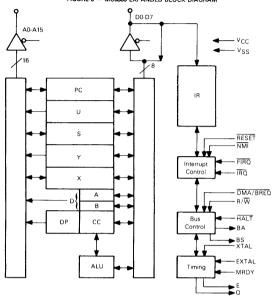

#### 6809 CHIP STRUCTURE

The 6809 chip structure is shown in Fig. 1-6 in summary to the discussion just completed. You should now have a basic understanding of each functional region and the associated control features of the 6809 and 6809E. In addition, you should now be aware of the architectural, software, and hardware improvements of the 6809 and 6809E over the 6800. In the chapters that follow we will discuss each of these new features in detail, beginning with the 6809's addressing modes and its instruction set

#### **REVIEW QUESTIONS**

| 1.         | Compatibility between the 6800 and 6809 instruction set exists at what level?                                   |

|------------|-----------------------------------------------------------------------------------------------------------------|

| 2.         | How many basic instructions are contained in the 6809 instruction set?                                          |

| 3.         | How many different addressing modes does the 6809 utilize?                                                      |

| 4.         | The 6809 was designed primarily for the market.                                                                 |

| <b>5</b> . | Two prime design considerations for the 6809 are: and                                                           |

| 6.         | The most advanced processor in the Motorola 8-bit family is the                                                 |

| 7.         | The most advanced microcomputer in the Motorola 8-bit family is the                                             |

| 8.         | What is the fundamental difference between the 6809 and 6809E?                                                  |

| 9.         | List the additional registers present in the 6809 architecture which do not exist in the 6800.                  |

| 10.        | The two new condition code flags and their bit positions in the CC                                              |

|            | register are: and                                                                                               |

| 11.        | Which of the internal 6809 registers are indexible and can therefore be used with the index mode of addressing? |

| 12.        | When an instruction points to an address of the address of an operand,                                          |

|     | this is called addressing.                                                                                                                                |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13. | What is the branching range of the $6809$ and how does this compare to the $6800$ ?                                                                       |

| 14. | What is the difference in the direct addressing mode for the $6809$ versus the $6800$ ?                                                                   |

| 15. | A 3.2-MHz crystal would produce aMHz 6809 clock frequency.                                                                                                |

| 16. | With the 6809's fast interrupt request (FIRQ) only the and                                                                                                |

|     | registers are stacked.                                                                                                                                    |

| 17. | The quadrature clock signal (Q) is the same frequency as the enable clock signal (E); however, Q leads E by what amount?                                  |

| 18. | When a valid memory address is not present from the 6809, what is the status of the address bus?                                                          |

| 19. | The 6809 replaces the 6800 three-state control line (TSC) with                                                                                            |

| 20. | The two extra control lines available on the $6809E$ which are not available                                                                              |

|     | on the 6809 are: and                                                                                                                                      |

|     | ANSWERS                                                                                                                                                   |

| 1.  | Source code (mnemonic)                                                                                                                                    |

| 2.  | 59                                                                                                                                                        |

| 3.  | 19                                                                                                                                                        |

| 4.  | Systems                                                                                                                                                   |

| 5.  | Position-independent code and 6800 compatibility                                                                                                          |

| 6.  | 6809                                                                                                                                                      |

| 7.  | 6801                                                                                                                                                      |

| 8.  | The 6809E is an off-chip clock version of the 6809.                                                                                                       |

| 9.  | Accumulator D (D) Direct page register (DP) Y index register (Y) User stack pointer (U)                                                                   |

| 10. | F (bit 6)<br>E (bit 7)                                                                                                                                    |

| 11. | All the index registers and stack pointers (X, Y, S, and U)                                                                                               |

| 12. | Indirect                                                                                                                                                  |

| 13. | The 6809 can branch anywhere within the 64K memory map using long relative addressing where the 6800 is limited to a plus $127_{10}$ and minus $128_{10}$ |

byte branching range.

- 14. With the direct addressing mode the 6809 can access any part of the 64K memory map using the direct page register (DP), where the 6800 is limited to the first 256 bytes of memory (page 0).

- 15. 0.8 MHz

- 16. Program counter (PC) and condition code (CC)

- 17. One-quarter cycle (90°)

- 18. The 6809 address is FFFF<sub>16</sub> during any clock signal when it is not using the bus structure.

- 19. Direct memory access request (DMA REQ)

- 20. Busy and last instruction cycle (LIC)

#### CHAPTER 2

### 6809 Addressing Modes

#### INTRODUCTION

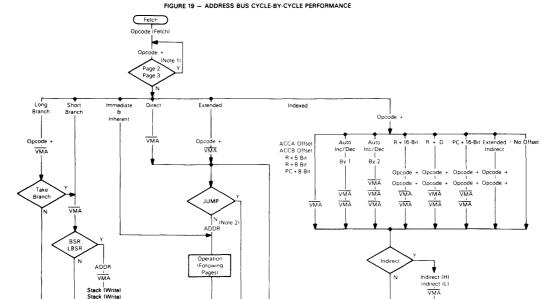

You are about to see what makes the 6809 a super microprocessor. As was mentioned earlier, it is not the mere number of instructions in an instruction set that makes one processor more powerful than another but a more important consideration: how many different ways the processor can utilize the fundamental instructions available to it. Instructions can access and operate on data in different ways by using different addressing modes. The 6809 has 59 instructions which utilize ten fundamental addressing modes, bringing the total number of unique operations to 1464. The ten fundamental addressing modes available to the 6809 are: inherent (implied), immediate, direct, extended, branch relative, indexed, extended indirect, program counter relative, indexed indirect, and register.

In addition, variations of these ten fundamental modes actually bring the total number of unique addressing modes to 19. For example, one of the most powerful addressing modes, indexed addressing, has five options: zero offset, constant offset (5-, 8-, or 16-bit), accumulator offset (A, B, or D) and auto-increment or auto-decrement (by 1 or 2). All of these options can access data indirectly using indexed indirect addressing. Indirect addressing means to address a memory location that contains the address of the operand rather than the operand itself. Thus, the instruction accesses the address of the operand, which in turn accesses the operand. Indirect operations are also available with the extended and program counter relative addressing modes.

As with the 6800, relative addressing is used with branch operations. With the 6809, however, relative addressing can also be used

to access and operate on memory data. It is also available in two versions: short relative (8-bit offset) and long relative (16-bit offset). Thus 6809 programs can be written with complete *position independence*.

Finally, *register addressing* will allow you to transfer to, or exchange, data between any two like-size registers within the 6809's architecture.

You might be wondering how an 8-bit machine can perform so many unique operations and, given an instruction, how do you specify which addressing mode is to be used? The answer is found in a *post byte*. A post byte is used with indexed, indexed indirect, extended indirect, program counter relative, and register addressing. The post byte follows the instruction op code in the instruction statement. It is used to specify the addressing mode and which internal register is to be used in the operation. With register addressing it is used to specify which two like-size registers are to be used in the transfer or exchange of data.

It is very important that you understand how to use the post byte and, for that matter, all the concepts presented in this chapter such that you can take full advantage of all of the 6809's capabilities. Once a full understanding of the addressing modes is achieved, you will be ready to apply these modes to the 6809 instruction set presented in Chapters 3, 4, and 5.

#### **OBJECTIVES**

At the end of this chapter you will be able to do the following:

- State the difference between direct addressing for the 6809 versus direct addressing for the 6800.

- Explain the role of the direct page register in direct addressing for the 6809.

- List the ten fundamental 6809 addressing modes.

- Explain how to use program counter relative addressing.

- Describe the four basic forms of indexed addressing.

- Understand how to use a post byte for indexed, program counter relative, extended, and register addressing.

- Interpret the meaning of a given post byte.

- Determine the required post byte for a given addressing situation.

- Define indirect addressing.

- Determine the effective operand address for instructions using indirect addressing.

- Understand assembly language symbols used for the various 6809 addressing modes.

# INHERENT, IMMEDIATE, AND EXTENDED ADDRESSING Inherent Addressing

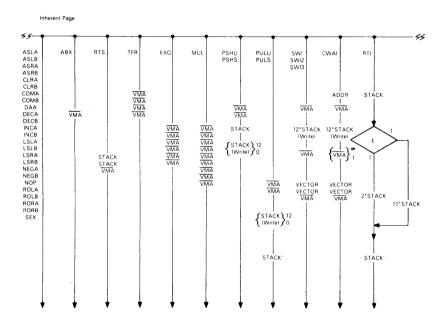

Inherent addressing, also referred to as implied addressing, is the simplest type of addressing since it only involves 1-byte instructions. Instructions involving the accumulators, such as increment, decrement, clear, shift (left or right), complement, etc., fall into this category. This type of addressing is also sometimes referred to as accumulator addressing when the instruction involves an operation on one of the accumulators. The format for inherent addressing is the same as that for the 6800 and most of the same instructions are involved.

#### Immediate Addressing (#)

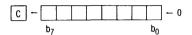

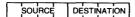

As with the 6800 the 6809 uses immediate addressing when the operand immediately follows the instruction op code. Therefore this type of addressing includes the data operand within the instruction statement. Operations involving the accumulators and index registers, such as load, add, subtract, AND, OR, compare, etc., can all utilize immediate addressing. When the immediate operation involves accumulator A or B, the instruction will be 2 bytes: a 1-byte instruction op code followed by the 1-byte operand. When the operation involves a 16-bit register, accumulator D or one of the index registers (X, Y, S, or U), the instruction will be 3 or 4 bytes; a 1- or 2- byte instruction op code (depending upon the particular instruction, refer to Chapter 3) followed by a 2-byte operand. With the 6800, op codes were never more than 1 byte in length; however, with the 6809 you will frequently see 2-byte instruction op codes, especially where the 16-bit registers are involved. This is necessitated since, with the 6809, there are more than 256 unique executable instructions. Also, a 2-byte operand is required when a 16-bit register is involved. The immediate addressing format is shown in Fig. 2-1A.

#### **Extended Addressing (\$\$)**

Extended addressing is used to access memory. Here, the memory address of the data operand follows the instruction op code. Extended addressing is used to access the full 64K memory address

| INSTRUCTION OP CODE |

|---------------------|

| (1 OR 2 BYTES)      |

| DATA OPERAND        |

| (1 OR 2 BYTES)      |

| INSTRUCTION OP CODE |

|---------------------|

| (1 OR 2 BYTES)      |

| HI ADDRESS BYTE     |

| LO ADDRESS BYTE     |

(A) Immediate addressing.

(B) Extended addressing.

Fig. 2-1. Immediate and extended addressing formats.

map, and therefore the address is 2 bytes in length: a HI address byte followed by a LO address byte. The instruction op code will be 1 or 2 bytes, depending on the particular instruction involved. Therefore 6809 instructions using extended addressing will be a total of 3 or 4 bytes in length. The instruction format for extended addressing is shown in Fig. 2-1B. Another form of extended addressing, extended indirect, will be discussed later in this chapter.

# DIRECT ADDRESSING AND THE DIRECT PAGE REGISTER (\$)

In the 6800, direct addressing was used to access operands that were stored in the first 256 bytes of memory (addresses 0000-00FF). Recall that when accessing this area of memory it was advantageous to use direct addressing over extended addressing, since fewer instruction bytes are used. For example, consider the following instruction codes:

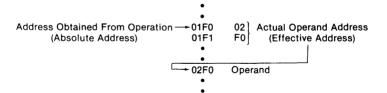

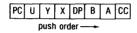

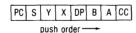

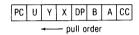

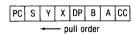

These instructions accomplish the same function, i.e., load accumulator A with the contents of memory address C7. However, instruction No. 1 uses direct addressing while instruction No. 2 uses extended addressing. The obvious advantage is that direct addressing requires only 2 instruction bytes while extended addressing requires 3. In addition, more MPU cycles would be required to execute the instruction using extended addressing. Therefore, direct addressing is used whenever operands are located in low memory. The drawback to the use of direct addressing in the 6800 is that you are limited to addressing the first 256 bytes of memory (00-FF) in this way. An operand residing in higher memory would require the use of extended addressing. However, the 6809 design engineers have eliminated this problem by including a direct page register (DPR) as part of the 6809's architecture. The direct page register essentially forms the most significant byte of the effective address. The least significant address byte is part of the instruction. When in the direct addressing mode the 6809 simply looks to the DPR for the most significant address byte and relies on the instruction to supply the least significant address byte. Therefore, to access the data located at address 00C7, as in the previous example, the direct page register would contain 00 (all zeros) and the 2-byte instruction

would be used. If, however, the DPR contained 01, the same instruction would access address 01C7. This eliminates the need to use extended addressing when you are accessing addresses above 00FF.

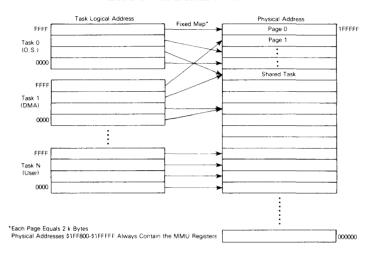

Some terminology is useful here. When the DPR contains 00, we say it is accessing page zero; when the DPR contains 01, it is accessing page 1, and so on, up to page 255 (FF). Note that the DPR can be used to access 256 pages (including page zero). Each page contains 256 address bytes. In other words, the DPR can be used to "page" through the entire 6809 address map, since 256 pages with 256 address bytes per page equals 64K address bytes, or the total 6809 map. A common application of the DPR is in high-level languages where global variables are accessed frequently. A global variable is a variable whose value is accessible throughout an entire program, in contrast to a local variable, whose value is accessible only in the program block (or subroutine) in which it is defined. In a subroutine the DPR can be used to "point" to a page containing the global variables, with the stack containing local variables. No problems arise as long as the language compiler keeps track of the DPR value. The DPR can also be used for multitasking operations. Multitasking is when several separate but interrelated tasks operate within a single program. In this application each task will be allocated a different page by the main program and accessed via the DPR. When writing programs you must be very careful in using the DPR since it is very easy to lose track of its value. But, when the DPR is used properly, you can generate very efficient, byte-saving programs.

After the 6809 is reset, the DPR contains all zeros (page zero) and the 6809 direct addressing mode will perform just as it would in the 6800. As you will see in Chapter 3 the DPR contents can then be easily modified to point to any page within the 6809's memory map.

#### **RELATIVE ADDRESSING**

There are two types of relative addressing available to the 6809. They are branch relative and program counter relative. By using these relative addressing modes you will be able to write complete position-independent programs for the 6809. A discussion of branch relative addressing will be provided first since it is very similar to the branching operation used in the 6800. Then a complete discussion of program counter relative addressing will be provided.

#### **Branch Relative Addressing**

Recall that the 6800 uses relative addressing for its branch instructions. The branch instruction op code is followed by a 1-byte twos complement (signed) relative address offset. Upon execution of the

branch the offset is added to the program counter's contents to form the branch destination address.

#### Example 2-1: Determining Forward Branch Destinations

Given a branch instruction located at address 002B with a relative address offset of 6F, determine the branch destination.

Since the branch instruction is 2 bytes (op code followed by the relative address offset), the program counter contains 002B+2 = 002D. The destination equals the program counter contents plus the offset, or 002D+006F = 009C.

#### Example 2-2: Determining Backward Branch Destinations

Consider a branch instruction located at address 002B as in the previous example. The relative address offset, however, is now F7. Determine the branch destination.

The program counter contents are 002D (refer to Example 2-1). Since the most significant bit of the twos complement offset is a logic 1, it is negative and the 6809 will branch backward. To obtain the destination the twos-complement offset is added to the program counter's contents. Therefore the destination address is 002D+FFF7 = 0024. Here the two most significant hex digits (FF) of the offset are implied since the offset is negative.

Refer to Table 2-1 for determining the 8-bit relative address offset required to branch to a given destination.

A serious limitation arises with this type of branching: since the signed offset is only 1 byte, with the most significant bit of that byte used to determine branching direction (forward or backward), you are limited to a range of  $-128_{10}$  to  $+127_{10}$  branching addresses, with respect to the branch operation. This is called *short branching*. To branch beyond this range with the 6800 would require branching to a branch or the use of a jump instruction. But, by using a jump, position independence is lost, which is a serious consequence, especially for high-level language programming, since an absolute address location is specified. However, if the relative address offset were 2 bytes, branches within a -32,768<sub>10</sub> to 32,767<sub>10</sub> range could be accomplished, thus allowing branching anywhere within the entire memory map while maintaining position independence throughout the program. This has been done with the 6809 while maintaining the short-branch instructions for byte efficiency when only short branches are required.

The 6809 adds a series of long-branch instructions which use a 2-byte signed relative address offset. The 6809 long-branch instructions contain a 2-byte op code followed by a 2-byte signed offset. Therefore, long-branch instructions are 4 bytes in length as compared with the 2-byte short-branch instructions.

Table 2-1, 6809 Short-Branch Calculator Table

| MSH-B  | F  | E  | D  | С  | В  | Α  | 9   | 8   |       |

|--------|----|----|----|----|----|----|-----|-----|-------|

| LSH-B  |    |    |    |    |    |    |     |     | LSH-F |

| -      | -  | 16 | 32 | 48 | 64 | 80 | 96  | 112 | 0     |

| F      | 1  | 17 | 33 | 49 | 65 | 81 | 97  | 113 | 1 1   |

| E      | 2  | 18 | 34 | 50 | 66 | 82 | 98  | 114 | 2     |

| D      | 3  | 19 | 35 | 51 | 67 | 83 | 99  | 115 | 3     |

| С      | 4  | 20 | 36 | 52 | 68 | 84 | 100 | 116 | 4     |

| В      | 5  | 21 | 37 | 53 | 69 | 85 | 101 | 117 | 5     |

| A      | 6  | 22 | 38 | 54 | 70 | 86 | 102 | 118 | 6     |

| 9      | 7  | 23 | 39 | 55 | 71 | 87 | 103 | 119 | 7     |

| 8<br>7 | 8  | 24 | 40 | 56 | 72 | 88 | 104 | 120 | 8     |

| 7      | 9  | 25 | 41 | 57 | 73 | 89 | 105 | 121 | 9     |

| 6      | 10 | 26 | 42 | 58 | 74 | 90 | 106 | 122 | A     |

| 6<br>5 | 11 | 27 | 43 | 59 | 75 | 91 | 107 | 123 | В     |

| 4      | 12 | 28 | 44 | 60 | 76 | 92 | 108 | 124 | С     |

| 3      | 13 | 29 | 45 | 61 | 77 | 93 | 109 | 125 | D     |

| 2      | 14 | 30 | 46 | 62 | 78 | 94 | 110 | 126 | E     |

| 1      | 15 | 31 | 47 | 63 | 79 | 95 | 111 | 127 | F     |

| 0      | 16 | 32 | 48 | 64 | 80 | 96 | 112 | -   | -     |

|        | 0  | 1  | 2  | 3  | 4  | 5  | 6   | 7   | MSH-F |

<sup>1.</sup> Count the number of bytes (in decimal) from the instruction following the branch to the branch target instruction,

Examples: Back 15<sub>10</sub> bytes F1<sub>16</sub>, Forward 77<sub>10</sub> bytes = 4D<sub>16</sub>, Back 107<sub>10</sub> bytes = 95<sub>16</sub>.

4 Kev

MSH-B = Most significant hex-backward LSH-B = Least significant hex-backward MSH-F = Most significant hex-forward LSH-F = Least significant hex-forward

Courtesy Mr. Ray Boaz, 1516 Jarvis Pl., San Jose, Calif. 95118

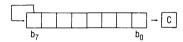

Both the 6809 long- and short-branch instruction formats are shown in Fig. 2-2. The short-branch instruction format shown in Fig. 2-2A is the same as that required for the 6800. The long-branch instruction format shown in Fig. 2-2B requires a 2-byte op code followed by the 2-byte signed offset. The high offset byte is first, followed by the low offset byte.

BRANCH INSTRUCTION OP CODE

(1 BYTE)

RELATIVE ADDRESS OFFSET

(1 BYTE)

| BRANCH INSTRUCTION OP CODE<br>(1ST BYTE) |

|------------------------------------------|

| BRANCH INSTRUCTION OP CODE (2ND BYTE)    |

| RELATIVE ADDRESS OFFSET<br>(HI BYTE)     |

| RELATIVE ADDRESS OFFSET<br>(LO BYTE)     |

- (A) Short-branch instruction format.

- (B) Long-branch instruction format (except for long branch always and subroutine).

Fig. 2-2. 6809 branch instruction formats.

<sup>2.</sup> Find this number inside the table.

Read this hexadecimal equivalent.

a. Top and left for branching backward.

b. Bottom and right for branching forward.

#### Example 2-3: Determining Long-Branch Destinations

Given a branch instruction located at address 5000 with a relative address offset of 02F0, determine the branch destination.

Since the long branch instruction is 4 bytes (a 2-byte op code followed by a 2-byte signed offset), the program counter contains 5000+4=5004. The destination equals the program counter's contents plus the offset, or 5004+02F0=52F4.

Now, suppose the offset were F2F0. Then, since the most significant bit of the offset is a logic 1, the 6809 will branch backward. As with short branches, to obtain the destination, add the twos complement offset to the program counter's contents. Therefore the destination address is 5004+F2F0 = 42F4.

#### Program Counter Relative (PC Relative) Addressing

To allow complete position-independent programs to be written without a lot of software overhead, the 6809 includes program counter relative addressing. With this type of addressing the address of an operand located in memory can be determined *relative* to the program counter's contents. With PC relative addressing an 8- or 16-bit signed offset is added to the program counter's contents to create the effective address of the operand, or the effective address of the address of the operand. (The latter case is referred to as indirect addressing, and will be discussed later.) Therefore data can be accessed anywhere within the 6809's memory map, relative to the program counter contents, thus allowing for complete position-independent programs.

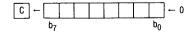

The instruction format required for program counter relative addressing is shown in Fig. 2-3. Note that the instruction can be 3 or 4 bytes in length, depending on the offset desired. Both 8- and 16-bit offsets are allowed. In either case a post byte follows the instruction op code. The offset byte(s) then follows the post byte. When this type of addressing is used, the program counter is used as a pointer register with an 8- or 16-bit offset; thus program counter relative

| INSTRUCTION OP CODE<br>(1 OR 2 BYTES) |

|---------------------------------------|

| POST BYTE                             |

| ± OFFSET                              |

| (1 OR 2 BYTES)        |  |

|-----------------------|--|

| POST BYTE             |  |

| ± OFFSET<br>(HI BYTE) |  |

| OFFSET<br>(LO BYTE)   |  |

INSTRUCTION OF CODE

(A) 8-bit signed offset.

(B) 16-bit signed offset.

Fig. 2-3. Program counter relative addressing.

addressing can be thought of as a type of indexed addressing. As you will see in Chapter 3 any instructions which use indexed addressing can also use program counter relative addressing. Since program counter addressing is considered a type of indexed addressing, a post byte is required to designate that the program counter register is being used as the pointer register rather than one of the indexible registers (X,Y,S,U). The use of the post byte will be discussed in more detail in the next section, on indexed addressing.

The following examples illustrate program counter relative addressing.

Example 2-4: Using Program Counter Relative Addressing With an 8-Bit Signed Offset

Consider the following instruction mnemonic sequence:

```

00FF

0100 LDA (instruction op code)

0101 post byte

0102 10 (8-bit offset)

0103 . .

```

The instruction is to load accumulator A with the contents of the memory address determined by adding the signed offset to the program counter's contents. The signed offset is  $10_{16}~(0001~0000_2)$  and the post byte specifies that the program counter is to be the pointer register. Recall that the program counter always points to the *next* instruction to be executed. Therefore, the program counter's contents are 0103 at this point in the program. Thus the operand to be loaded into accumulator A is located at address 0103+0010=0113. In this example the offset was positive since its most significant bit is 0. However, if the most significant bit of the offset is 1, the *twos complement* offset is negative. For example, if the offset were F0 (1111 0000<sub>2</sub>), the effective operand address would be 0103+FFF0=00F3.

# Example 2-5: Using Program Counter Relative Addressing With a 16-Bit Signed Offset

Consider the following instruction mnemonic sequence:

| 0103 | FF | (offset | LO | byte) |

|------|----|---------|----|-------|

| 0104 | •  |         |    |       |

|      |    |         |    |       |

This instruction will load accumulator B with the contents of the memory location formed by adding the 16-bit offset (01FF) to the program counter's contents. The program counter contains 0104 at this point in the program. Therefore the effective operand address is 0104+01FF=0303.

#### INDEXED ADDRESSING

You can probably recall that indexed addressing is the most powerful form of addressing available to the 6800. It became extremely valuable when operating on data located in consecutive memory locations. In the 6800 the indexed addressing instruction is a 2-byte instruction consisting of the instruction command followed by a signed indexed offset. To form the effective operand address the 6800 adds the offset to the contents of the 16-bit index register. Several 6800 instructions are associated with the index register. Recall also that you can increment, decrement, load, store and transfer the index register contents to and from the stack pointer. A substantial amount of programming power was gained by including the index register within the 6800's architecture.

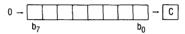

Now, with the 6809, the indexed addressing mode has been enhanced by the inclusion of four 16-bit registers which may be used as pointer registers in the indexed mode of addressing. As mentioned in Chapter 1 these registers are the X, Y, S, and U registers (refer to Fig. 1-3). With the 6809 there are four basic forms of indexed addressing that can be used with these registers. They are: zero-offset indexed, constant-offset indexed, accumulator-offset indexed, and auto-increment/decrement indexed.

The instruction format for indexed addressing is shown in Fig. 2-4. You see that the instruction op code is *always* followed by a *post byte*, which in turn may or may not be followed by an *offset*. The *post byte* of an indexed instruction specifies the basic form of in-

| INSTRUCTION OP CODE |

|---------------------|

| (1 OR 2 BYTES)      |

| POST BYTE           |

| OFFSET              |

| (1 OR 2 BYTES)      |

Fig. 2-4. General indexed addressing instruction format.

dexed addressing to be used as well as the specific pointer register that will be used in determining the effective operand address. Indexed addressing can be used with 31 of the 59 instructions of the 6809.

Now let us discuss each basic type of indexed addressing; then, we will learn how to use the post byte. Examples of each indexed mode are provided at the end of this chapter.

#### **Zero-Offset Indexed Addressing**

This type of indexed addressing allows the pointer register to point directly to the effective operand address, since the offset is zero. In other words, the specified pointer register contains the address of the operand to be used in the operation. These instructions will be 2 or 3 bytes: the instruction op-code byte(s) $^{\circ}$  followed by the post byte. The post byte will specify the zero-offset mode and the pointer register to be used. This mode of indexed addressing is the fastest since a minimum number of bytes is required and no offset calculation is required.

#### **Constant-Offset Indexed Addressing**

This form of indexed addressing is very similar to the 6800's indexed addressing. However, any of the pointer registers (X, Y, U, or S) can be used and the signed offset can be 5, 8, or 16 bits. The post byte will follow the instruction op code and will specify the pointer register and the offset size. When a 5-bit signed offset is used, the offset is included as part of the post byte and therefore the 5-bit offset is most efficient in the use of bytes and MPU cycles as compared with the other constant-offset versions. Also, the offset is a twos complement (signed) value with the most significant bit (msb) of the offset used to determine its sign. If the most significant bit is a logic 0, the offset will be positive, and if the most significant bit is a logic 1, the offset will be negative. Therefore, the 5-bit offset reduces to a  $\pm 4$ -bit offset with a corresponding offset range of from  $-16_{10}$  to  $+15_{10}$ .

If an 8-bit offset is desired, the instruction will be 3 or 4 bytes in length. Here the instruction op-code byte(s)\* is followed by the post byte, which in turn is followed by the 8-bit offset byte. The post byte will specify constant-offset indexed addressing and the pointer register to be used. The offset byte is then added to the pointer register contents to determine the effective address. Again, the offset is a twos complement (signed) value with the msb used to determine the sign. Therefore the 8-bit offset reduces to a  $\pm 7$ -bit offset with a corresponding range of from  $-128_{10}$  to  $+127_{10}$ .

<sup>\*</sup> With the 6809 some instructions require 2 op-code bytes.

If a 16-bit offset is desired, the post byte will be followed by 2 offset bytes. The most significant offset byte will be first, then the least significant byte. To determine the effective address, the 16-bit signed offset will be added to the pointer register specified by the post byte. Since the offset is signed, it reduces to  $\pm 15$  bits with a corresponding range of from  $-32,768_{10}$  to  $+32,767_{10}$ .

#### **Accumulator-Offset Indexed Addressing**

This type of indexed addressing is similar to the constant-offset mode, except that the contents of one of the accumulators (ACCA, ACCB, or ACCD) are added to the specified index register (X, Y, S, or U) to obtain the effective address. The obvious advantage here is that the offset can be calculated just prior to the indexed operation. The instruction will be 2 or 3 bytes in length: the instruction op-code byte(s) followed by the post byte. The post byte will specify the accumulator-offset mode, pointer register, and which accumulator is to be used. The 6809 uses the twos complement (signed) value of the specified accumulator to determine the effective address. Neither the specified accumulator or index register contents are affected by the offset calculation.

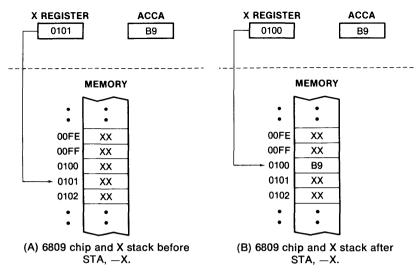

#### **Auto-Increment/Decrement Indexed Addressing**

This mode of indexed addressing is a blessing, since it eliminates the need to increment/decrement the index register with a separate instruction when stepping through memory tables and moving blocks of data within memory. In the auto-increment mode the specified pointer register contains the address of the first operand. Then, after the first operand is used in the operation specified by the op code, the pointer register is automatically incremented to point to the next consecutive operand address and so on, as many times as the instruction is executed. Therefore, memory data are fetched consecutively from a low to a higher memory address. In the auto-decrement mode, memory data are fetched from a high to a lower memory address since the specified pointer register is automatically decremented just prior to the operand's being fetched. The auto-increment is therefore a post-increment operation and the auto-decrement a pre-decrement operation. Thus, if you are using the auto-decrement option, the starting address must be n+1 to fetch information from address n. The increment/decrement can be either by 1 or 2 to allow for 8- or 16-bit data.

The auto-increment/decrement instruction will be 2 or 3 bytes in length: the instruction op-code byte(s) followed by the post byte. The post byte will specify auto incrementing or decrementing, the pointer register to be incremented or decremented, and the amount of increment or decrement (1 or 2).

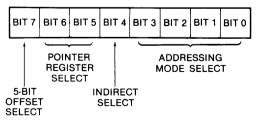

#### POST BYTE

From the previous discussion it is obvious that the post byte plays an important role in the indexed addressing mode. In addition, you saw that a post byte was also required when using program counter relative (PC relative) addressing. In summary, you should have discovered from previous discussions that:

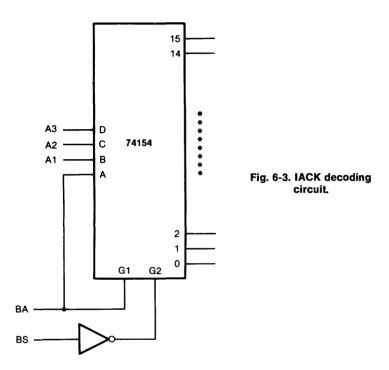

- 1. The post byte is used to specify one of the following modes of addressing: